Cache

Vyrovnávací paměť - cache - je velmi rychlá paměť relativně malé kapacity, sloužící ke zrychlení toku dat mezi procesorem a operační pamětí, resp. jinými částmi počítače. Je zapojena mezi procesor a operační paměť a to jak uvnitř procesoru (486DX) nebo vně procesoru. Mohou být zapojeny současně jak vnitřní tak i vnější cache.

Používá se pro zrychlení toku dat, nejčastěji mezi operační pamětí a µP. Mají malou inteligenci – dovedou o něčem rozhodnout sami. Je ovládána řadičem (firmware), který nemůžeme ovlivnit.

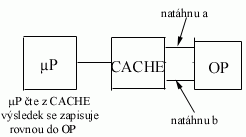

Přenos mezi µP a CACHE je po slovech (někdy i po dvojtých

slovech), mezi CACHE a operační pamětí je po blocích. Mezi µP a operační

pamětí slouží pouze pro čtení z hlediska procesu.

Přenos mezi µP a CACHE je po slovech (někdy i po dvojtých

slovech), mezi CACHE a operační pamětí je po blocích. Mezi µP a operační

pamětí slouží pouze pro čtení z hlediska procesu.

V

CACHE se přepisují hodnoty.

V

CACHE se přepisují hodnoty.

Je-li obsah na adrese paměti žádaný procesorem ve vyrovnávací paměti,

je tento obsah rychle předán procesoru. Není-li ve vyrovnávací paměti,

zavede se do ní celý blok po sobě jdoucích dat. Tento proces trvá déle

než přímý přístup do fyzické paměti a tedy zvýšení výkonu nastane

pouze tehdy, je-li počet úspěšných zásahů řádově větší než

neúspěšných. Při správné organizaci bývá úspěšnost až 97% .

Druhy CACHE

Podle přístupu:

- asynchronní – obsazují sběrnice po celou dobu

- synchronní – CPU po zadání adresy nečeká až se objeví data na sběrnici, ale o data požádá v dalším taktu, takže odpadá wait stav procesoru. Tím se zrychlí tok data průměrné zpoždění SRAM se sníží na 9 ns.

- synchronní – pipelined burst SDRAM CACHE (s hromadným přístupem) – synchronní CACHE, zadávání adresy je stejné, ale přenáší se několik dat za sebou – burst režim.

Podle způsobu vyhledávání:

- asociativní – vyhledávání podle (části) obsahu – část informace znám, podle této části vyhledám zbytek (vyhledávání např. *.pdf ve Win)

- neasociativní – vyhledávání podle adres, nepoužívá se

Podle vztahu k operační paměti:

- netransparentní – zastaralý, nevhodný, dnes se nepoužívá. Změna obsahu není zachycena do CACHE a CACHE pak neobsahuje správné údaje.

- transparentní – nutné u víceprocesorových systémů. Procesor (čipová sada) obsahuje další řadič, který sleduje spolu s CHIP SETem transakce na sběrnici a podle nich upravuje I (invalid) tagy v CACHE.

Podle počtu položek na 1 adresu:

Pružné části OP na jednom řádku.

- jednocestné – 1 blok

- dvoucestné – 2 bloky

- čtyřcestné – 4 bloky

- osmicestné – 8 bloků

Podle množství současných přístupů:

- jednoportové

- dvouportové

Podle adresace

- s fyzickou adresací - (obvykle umístěné mezi MMU a OP). Přepočet adres na fyzické trvání několik taktů a tak tato paměť je pomalejší. Nemůže nastat kolise adres.

- s virtuální nebo logickou adresací - (obvykle umístěné mezi CPU a MMU). Virtuální adresa je téměř ihned k dispozici a tedy vyhledávání je rychlé. U multiprocesorových systémů. U multitaskingu může stejná virtuální adresa znamenat různé fyzické adresy. Nutno ošetřovat cache.

Podle obsahu

- společná pro data a instrukce

- pouze pro data- datová

- pouze pro instrukce – instrukční

Podle umístění vzhledem k µP

- vnitřní (ondie) – na stejném chipu jako µP

- vnější – všechny ostatní CACHE

Podle pořadí od µP

- L(level)1 – CACHE první úrovně, nejblíž k µP, nejčastěji vnitřní, nejmenší, nejrychlejší, šířka sběrnice podle µP

- L2 – CACHE druhé úrovně, větší, pomalejší

- L3 – největší, nejpomalejší

L1, L2, L3 jsou rychlejší než OP.

Podle spolupráce s operační pamětí (OP)

- CACHE Write Through – zapisuje modifikovaná data v CACHE, zapisuje současně do CACHE a OP. Výstup na sběrnici je obvykle bufferován (FIFO délky 1 až 4), aby se nezdržoval proces čekání na ukončení zápisu.

- CACHE Write Back – zapisuje data pouze do CACHE. Do OP se provede zápis až při rušení obsahu CACHE. Rychlejší než Write Through. Nebezpečnější, protože nesouhlasí obsah CACHE a OP.

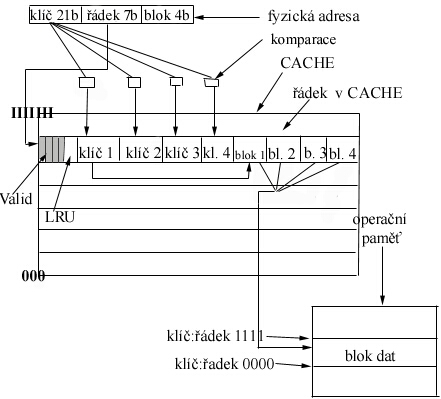

CACHE 486

Při hledání spočítám fyzickou adresu a pak hledám v

Cache.

Při hledání spočítám fyzickou adresu a pak hledám v

Cache.

Řádek ve fyz. adrese odkazuje na řádek v Cache. Na řádku

jsou adresy se stejnými 7b. Vyhl. řádku je neasociativní.

Na každém řádku v Cache paměti jsou čtyři klíče

(čtyřcestná paměť).

Komparace se provádí asociativním vyhledáváním a slouží

k vyhledávání klíčů.Ke každ. klíčí je přiřazena jeden blok dat.

Každý blok dat obsahuje 16B dat, které jsou na adrese OP.

Valid (4b) – každému klíči je zde přiřazen 1b, jestliže je klíč obsazený má tento bit hodnotu 1, jinak 0. Jestliže klíče nesouhlasí, obsadí se klíč, který má vyhledávat na volný klíč a přizpůsobí se volnému bloku dat, příslušný b ve valid se přepíše na 1. LRU (3b) – pokud nenajdu při komparaci správný klíč použiji LRU, který vyhledá nejdéle nepoužité klíče a zjistí, který klíč aktuálně nepotřebuje a přepíše ho zpět do OP. Nakonec vezme nový potřebný klíč. LRU není ideální, ale postačuje.